| <b>MARK 2/3</b> | Peripherals<br>Interface<br>Manual |  |

|-----------------|------------------------------------|--|

|                 |                                    |  |

|                 |                                    |  |

|                 |                                    |  |

|                 |                                    |  |

|                 |                                    |  |

|                 |                                    |  |

|                 |                                    |  |

|                 |                                    |  |

-

# DATA CORPORATION

# POINT 4<sup>™</sup> MARK 2/3 PERIPHERALS INTERFACE MANUAL

# **Revision D**

### NOTICE

Every attempt has been made to make this manual complete, accurate and up-to-date. However, all information herein is subject to change due to updates. All inquiries concerning this manual should be directed to POINT 4 Data Corporation.

Copyright <sup>©</sup> 1982, 1984 by POINT 4 Data Corporation (formerly Educational Data Systems, Inc). Printed in the United States of America. All rights reserved. No part of this work covered by the copyrights hereon may be reproduced or copied in any form or by any means--graphic, electronic, or mechanical, including photocopying, recording, taping, or information and retrieval systems -- without the prior written permission of:

> POINT 4 Data Corporation 15442 Del Amo Avenue Tustin, CA 92680 (714) 259-0777

# **REVISION RECORD**

### PUBLICATION NUMBER: HM-081-0027

| <u>Revision</u> | Description                                                                                  | Date     |

|-----------------|----------------------------------------------------------------------------------------------|----------|

| Α               | Initial Release                                                                              | 08/06/82 |

| В               | Update package incorporating information on the MARK 3B PIB                                  | 10/30/82 |

| С               | Update package incorporating information on the MARK 2 PIB                                   | 02/20/84 |

| D               | Update package incorporating information<br>relevant to the MARK 2 with floppy disk<br>drive | 12/01/84 |

## LIST OF EFFECTIVE PAGES

Changes, additions, and deletions to information in this manual are indicated by vertical bars in the margins or by a dot near the page number if the entire page is affected. A vertical bar by the page number indicates pagination rather than content has changed. The effective revision for each page is shown below.

| Page                      | Rev    | Page                    | Rev   | Page | Rev |

|---------------------------|--------|-------------------------|-------|------|-----|

|                           |        |                         |       |      |     |

| Cover                     | -      | 4-7 thru 4-37           | А     |      |     |

| Title                     | D      | 5-1, 5-2                | С     |      |     |

| ii                        | С      | 5-3                     | В     |      |     |

| iii, iv                   | D      | 5-4                     | С     |      |     |

| v/vi                      | С      | 5-5 thru 5-14           | В     |      |     |

| vii thru xi               | D      | 5-15, 5-16              | С     |      |     |

| xii                       | С      | 5-17 thru 5- <b>4</b> 0 | В     |      |     |

| xiii                      | D      | 5-41                    | С     |      |     |

| xiv                       | С      | 6-1 thru 6-28           | D     |      |     |

| XV                        | D      | Appendix Title          | -     |      |     |

| 1-1                       | D      | A-1                     | A     |      |     |

| 1-2 thru 1-4              | С      | B-1 thru B-8            | A     |      |     |

| 1-5                       | D      | C-1 thru C-12           | B     |      |     |

| 1-6 thru 1-9              | С      | Comment Sheet           | D<br> |      |     |

| 1-10, 1-11                | D      | Mailer<br>Dack Couer    | -     |      |     |

| 1-12 thru 1-30<br>2-1     | C<br>B | Back Cover              | ·     |      |     |

| 2-2, 2-3                  | C      |                         |       |      |     |

| 2-2, 2-3<br>2-4 thru 2-28 | Ă      |                         |       |      |     |

| 2-29                      | В      |                         |       |      |     |

| 2-30, 2-31                | Ā      |                         |       |      |     |

| 2-32                      | В      |                         |       |      |     |

| 3-1, 3-2                  | С      |                         |       |      |     |

| 3-3, 3-4                  | В      |                         |       |      |     |

| 3-5 thru 3-18             | А      |                         |       |      |     |

| 3-19                      | D      |                         |       |      |     |

| 3-20 thru 3-32            | A      |                         |       |      |     |

| 3-33 thru 3-35            | С      |                         |       |      |     |

| 3-36, 3-37                | A      |                         |       |      |     |

| 3-38, 3-39                | С      |                         |       |      |     |

| 3-40                      | D      |                         |       |      |     |

| 3-41, 3-42                | С      |                         |       |      |     |

| 3-43 thru 3-49            | A      |                         |       |      |     |

| 4-1 thru 4-6              | С      |                         |       |      |     |

|                           |        |                         |       |      |     |

HM-081-0027-D POINT 4 Data Corporation iv

MARK 2/3 Peripherals Manual

# PREFACE

This manual describes the peripheral interface functions supported by the POINT 4 MARK 2 or 3 Computer System. The peripheral functions are controlled by a Peripherals Interface Board (PIB). The PIB is available in three versions. All versions contain a built-in multiplexer and a disc drive interface. However, the disc drive interfaces are different on the MARK 2 and MARK 3 systems. In addition, the MARK 2 and the MARK 3 PIBs provide a tape drive interface. The MARK 3B PIB provides a floppy disc drive interface.

The introduction provides information regarding the characteristics, internal architecture, and input/output interface handling of each of the PIBs.

Separate sections are devoted to the multiplexer, the different disc drives, tape drive, and floppy disc drive interfaces. The appendices provide a table of ASCII codes, and both tape and floppy disc handling flowcharts.

Separate manuals describe the MARK 2/3 Computer System and provide step-by-step instructions for installation, upgrade and operating procedures.

Related manuals include:

|       |        | Title                    | Pub. Number |

|-------|--------|--------------------------|-------------|

| POINT | 4 MARK | 3 Computer System Manual | HM-081-0019 |

| POINT | 4 MARK | 3 Diagnostics Document   |             |

| POINT | 4 MARK | 2 Diagnostics Document   |             |

| POINT | 4 MARK | 3T Computer User Guide   | HM-081-0029 |

| POINT | 4 MARK | 2 Computer User Guide    | HM-081-0031 |

HM-081-0027-C POINT 4 Data Corporation abios.

# **CONTENTS**

| <u>Section</u>                                                                                                                                                                                      | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                                                                                                                                                                   | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.1 $1.1.1$ $1.1.2$ $1.1.2.1$ $1.1.2.3$ $1.1.2.4$ $1.1.2.5$ $1.1.2.6$ $1.1.2.7$ $1.2.7$ $1.2.1$ $1.2.1.1$ $1.2.1.2$ $1.2.1.1$ $1.2.1.2$ $1.2.2.1$ $1.2.3.1$ $1.2.3.1$ $1.2.3.2$ $1.2.3.3$ $1.2.3.4$ | GENERAL DESCRIPTION<br>System Description<br>Equipment Characteristics<br>Communications Control<br>Disc Drive Interface on MARK 3<br>and MARK 3B PIBs<br>Disc Drive Interface on a MARK 2 PIB<br>Tape Drive Interface on MARK 3<br>and MARK 2 PIBs<br>Floppy Disc Drive Interface<br>on a MARK 3B PIB<br>Floppy Disc Drive Interface<br>on a MARK 2 PIB<br>Input/Output Instructions<br>PIB Internal Architecture<br>INPUT/OUTPUT INTERFACE HANDLING<br>Program Interrupt and Priority Scheme<br>Interrupt Sequence<br>Programming Polling and Interrupts<br>Programmed I/O Transfers<br>Master Terminal Interface<br>Direct Memory Access Transfers<br>Enabling/Disabling DMA Transfers<br>Initiating DMA Transfer<br>Turning off Automatic Block Transfer Mode<br>for Disc, Tape or Floppy<br>Turning off Automatic Block Transfer Mode<br>for Multiplexer | $ \begin{array}{c} 1-1\\ 1-6\\ 1-8\\ 1-9\\ 1-9\\ 1-9\\ 1-9\\ 1-10\\ 1-10\\ 1-10\\ 1-11\\ 1-12\\ 1-16\\ 1-16\\ 1-17\\ 1-18\\ 1-25\\ 1-25\\ 1-25\\ 1-25\\ 1-29\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\ 1-30\\$ |

| 2                                                                                                                                                                                                   | MULTIPLEXER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.1<br>2.2<br>2.3<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.3.1<br>2.3.3.2<br>2.3.4<br>2.3.5                                                                                                                | INTRODUCTION<br>BAUD-RATE SELECTION<br>COMMUNICATIONS BYTE MODE<br>• Programmed I/O Instructions<br>UART Asynchronous Communications<br>Command Register<br>Standard Mode of Operation<br>Operational Mode Modifications<br>Status Register<br>Software Polling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-1<br>2-2<br>2-4<br>2-5<br>2-5<br>2-7<br>2-7<br>2-7<br>2-8<br>2-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.4                 | COMMUNICATIONS AUTO MODE                      | 2-12 |

|---------------------|-----------------------------------------------|------|

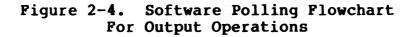

| 2.4.1               | MUX I/O Control Block                         | 2-12 |

| 2.4.2               | Control Word Definitions                      | 2-13 |

| 2.4.3               | Input Operations                              | 2-14 |

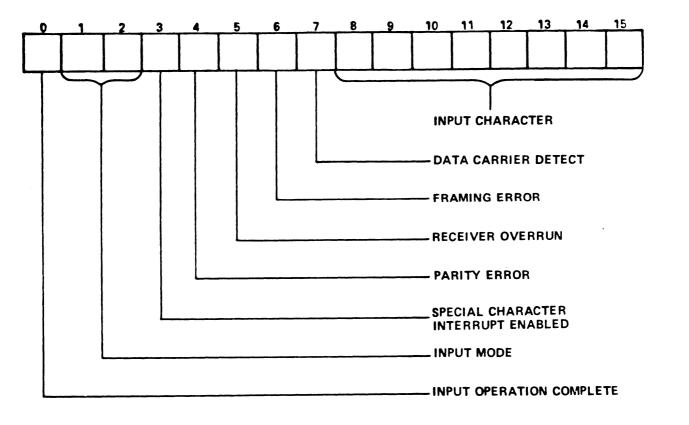

| 2.4.3.1             | Input Control Word                            | 2-14 |

| 2.4.3.2             | Input Termination Status                      | 2-19 |

| 2.4.3.3             | Input Byte Pointer                            | 2-19 |

| 2.4.3.4             | Last Input Byte                               | 2-19 |

| 2.4.4               | Output Operations                             | 2-20 |

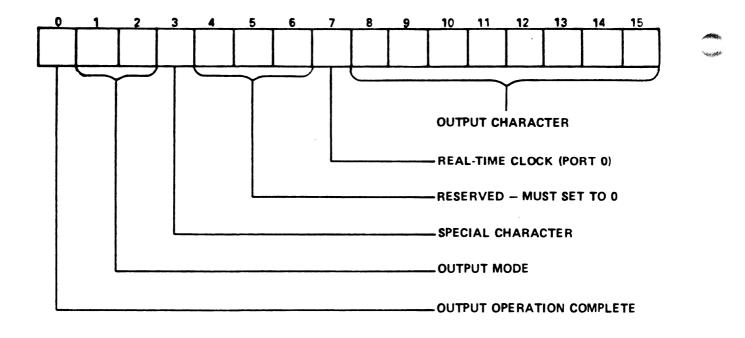

| 2.4.4.1             | Output Control Word                           | 2-20 |

| 2.4.4.2             | Output Termination Status                     | 2-24 |

| 2.4.4.3             | Output Byte Pointer                           | 2-25 |

| 2.4.4.4             | Last Output Byte                              | 2-25 |

| 2.5                 | INITIALIZATION PROCEDURES                     | 2-26 |

| 2.5.1               | Setting IOCB Starting Address                 | 2-26 |

| 2.5.2               | Initialization Guidelines                     | 2-27 |

| 2.5.3               | Enabling/Disabling Ports and Port Parameters  | 2-28 |

| 2.5.3.1             | Master Reset                                  | 2-28 |

| 2.5.3.2             | Port Initialization                           | 2-29 |

| 2.5.3.3             | Enabling/Disabling Transmitters and Receivers |      |

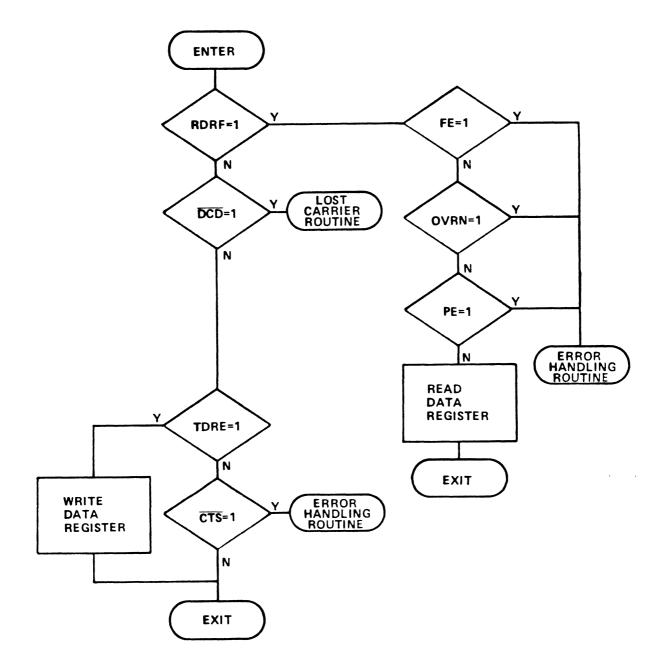

|                     | POLLING MUX INTERRUPT                         | 2-32 |

| 2.7                 | PAUSING MUX                                   | 2-32 |

| <b>-</b> • <i>i</i> |                                               |      |

|                     |                                               |      |

| 3                   | DISC DRIVE INTERFACE                          | 3-1  |

|                     |                                               |      |

| 3.1                 | INTRODUCTION                                  | 3-1  |

| 3.1.1               | Performance Characteristics                   | 3-2  |

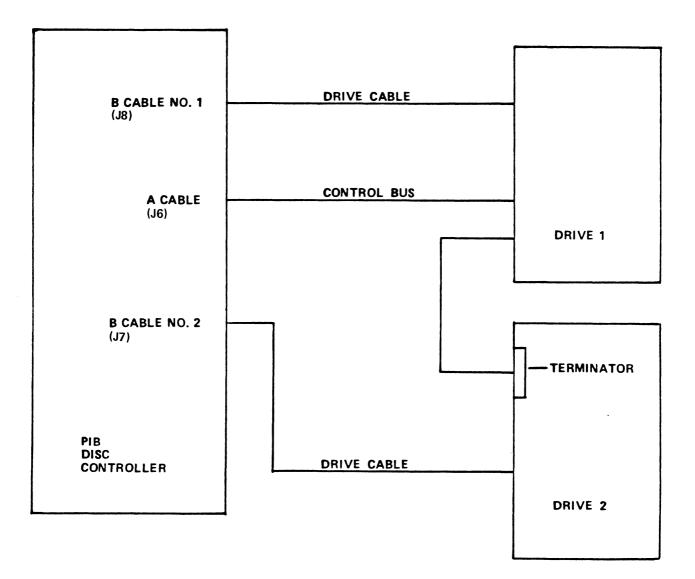

| 3.1.2               | Multi-Drive Connection                        | 3-3  |

| 3.1.3               | Disc Drive Cabling                            | 3-4  |

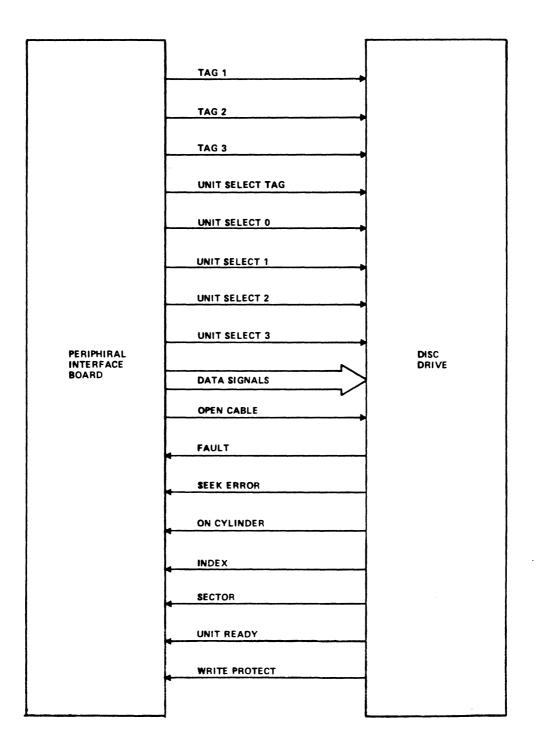

| 3.1.3.1             | Drive Control Bus (A Cable)                   | 3-4  |

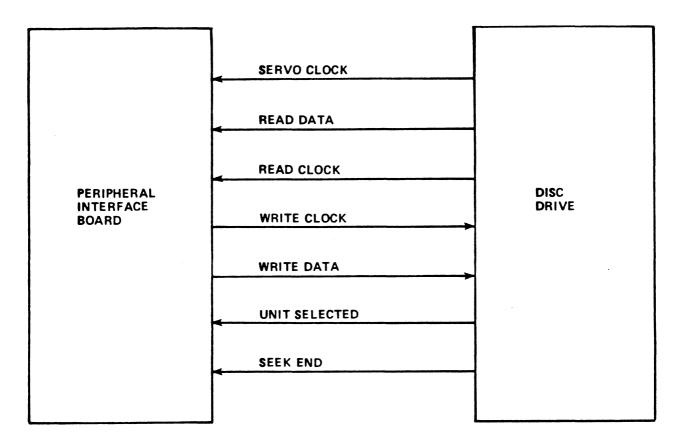

| 3.1.3.2             | Drive Cables (B Cables)                       | 3-9  |

| 3.2                 | PROGRAMMED INPUT/OUTPUT                       | 3-11 |

| 3.2.1               | Programmed I/O Input                          | 3-11 |

| 3.2.2               | Programmed I/O Output                         | 3-13 |

| 3.2.2.1             | DOA with Device Code 50 (Drive Unit Number)   | 3-13 |

| 3.2.2.2             |                                               | 3-14 |

| 3.2.2.3             |                                               | •    |

|                     | Loading)                                      | 3-15 |

| 3.2.2.3.            | l Tag l                                       | 3-16 |

| 3.2.2.3.            |                                               | 3-17 |

| 3.2.2.3.            | 3 Tag 3                                       | 3-18 |

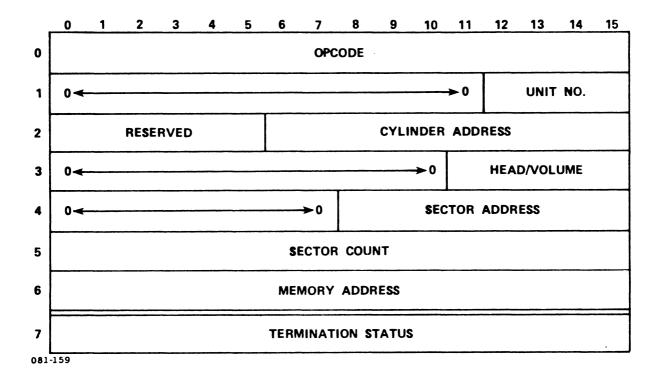

| 3.3                 | INPUT/OUTPUT CONTROL BLOCK (IOCB)             | 3-19 |

| 3.3.1               | Opcode (Word 0)                               | 3-19 |

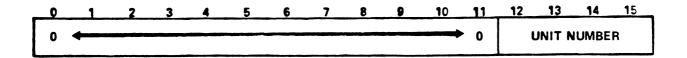

| 3.3.2               | Unit Number (Word 1)                          | 3-21 |

| 3.3.3               | Cylinder Address and Protect Flags (Word 2)   | 3-22 |

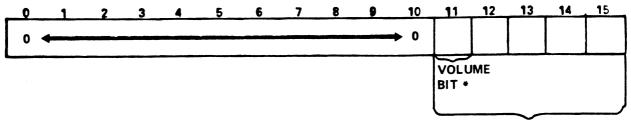

| 3.3.4               | Head/Volume (Word 3)                          | 3-23 |

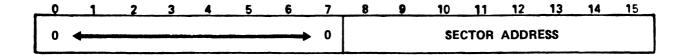

| 3.3.5               | Sector Address (Word 4)                       | 3-24 |

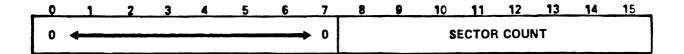

| 3.3.6               | Sector Count (Word 5)                         | 3-25 |

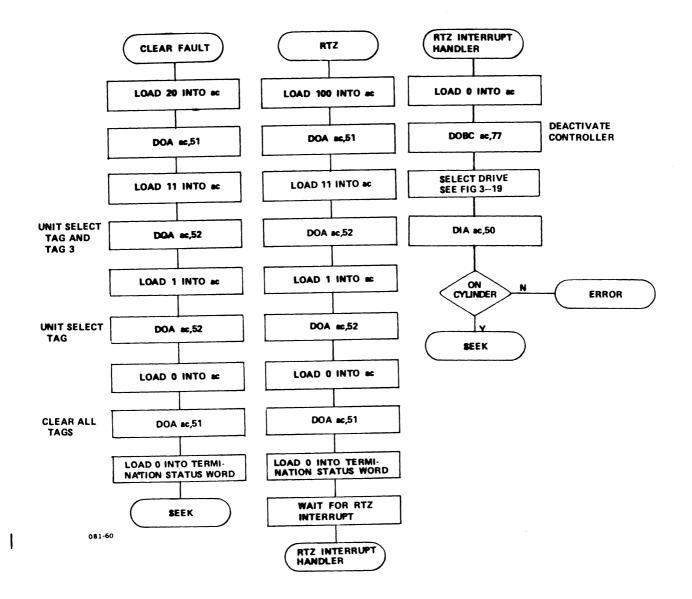

| 3.3.7               | Memory Address (Word 6)                       | 3-26 |

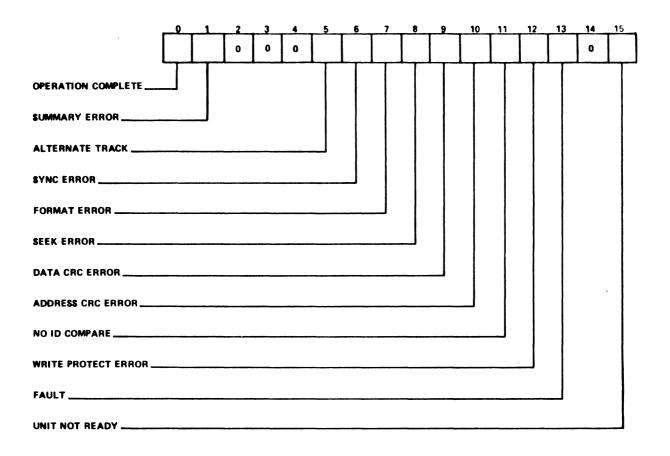

| 3.3.8               | Termination Status (Word 7)                   | 3-27 |

| 3.3.9               | Disc Controller Input Control                 | 3-30 |

| 3.3.10              | Disc Controller Output Control                | 3-31 |

| 2.2.10              | bibe concrotter output concrot                |      |

deresting. Nerright

| 3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.5<br>3.5.1<br>3.5.2<br>3.5.2.1<br>3.5.2.2<br>3.5.2.1<br>3.5.2.2<br>3.5.2.4<br>3.5.3<br>3.5.4<br>3.5.4.1<br>3.5.4.2<br>3.5.4.3<br>3.5.4.4<br>3.5.4.4<br>3.5.4.4 | Seek Initiation<br>Seek Error Recovery<br>SECTOR BLOCK FORMAT COMMANDS<br>Formatting Operation<br>Sector Block Description<br>Sector Block Format - Word 0 Functions<br>Sector Block Format - Word 1 Functions<br>Sector Block Format - Word 2 Functions<br>Sector Block Format - Word 3 Functions<br>Formatting Procedure<br>Sector Block I/O Operations<br>Write Data Operation<br>Read Data Operation<br>Read-Verify Operation<br>Read-Regardless Operation                                                                                                                                                                           | 3-32<br>3-32<br>3-36<br>3-37<br>3-39<br>3-40<br>3-40<br>3-40<br>3-41<br>3-42<br>3-43<br>3-44<br>3-46<br>3-46<br>3-46<br>3-46<br>3-47<br>3-47<br>3-49                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4                                                                                                                                                                                                  | QIC-02 STREAMING TAPE DRIVE INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-1                                                                                                                                                                                                                                                                                                     |

| 4.4.1<br>4.4.1.1<br>4.4.1.2                                                                                                                                                                        | Features<br>Performance Characteristics<br>TAPE CONTROLLER INTERFACE<br>Tape Controller Interface Signals<br>INPUT/OUTPUT CONTROL OPERATIONS<br>Programmed I/O Input<br>Status Byte Transfer<br>Programmed I/O Output<br>TAPE CONTROLLER IOCB<br>Tape Transfer Control<br>DOBP Instruction<br>DIBP Instruction<br>TAPE CONTROLLER COMMANDS<br>Select Command (Type 0)<br>Position Command (Type 1)<br>Write Command (Type 2)<br>End of Tape Handling<br>Write File Mark Command (Type 3)<br>Read Command (Type 4)<br>Read File Mark Command (Type 5)<br>Read Status Command<br>Exception Byte 0<br>2 Exception Byte 1<br>3 Bytes 2 and 3 | $\begin{array}{c} 4-1\\ 4-1\\ 4-2\\ 4-3\\ 4-3\\ 4-7\\ 4-7\\ 4-9\\ 4-10\\ 4-13\\ 4-14\\ 4-14\\ 4-14\\ 4-14\\ 4-15\\ 4-16\\ 4-17\\ 4-18\\ 4-19\\ 4-20\\ 4-20\\ 4-20\\ 4-20\\ 4-20\\ 4-21\\ 4-22\\ 4-23\\ 4-24\\ 4-27\\ 4-29\\ 4-29\\ 4-29\\ 4-29\\ 4-30\\ 4-30\\ 4-31\\ 4-32\\ 4-33\\ 4-34\\ \end{array}$ |

| 4.6.6<br>4.6.7<br>4.6.7.1<br>4.6.7.2<br>4.6.7.3<br>4.6.7.4<br>4.6.7.5                                                                                                                                                                                                                                                                                                                                                            | Read File Mark Operations<br>Error Processing and Recovery<br>Write Buffer Overrun<br>Read After Write Errors<br>Read Buffer Underruns<br>Read Data Errors<br>Read Sequence Errors                                                                                                                          | 4-34<br>4-35<br>4-35<br>4-36<br>4-36<br>4-37<br>4-37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5                                                                                                                                                                                                                                                                                                                                                                                                                                | FLOPPY DISC DRIVE INTERFACE                                                                                                                                                                                                                                                                                 | 5-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

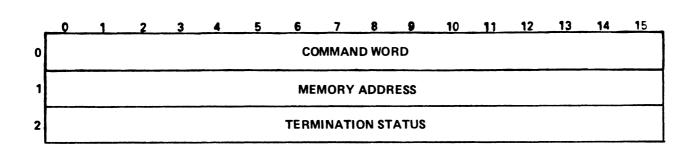

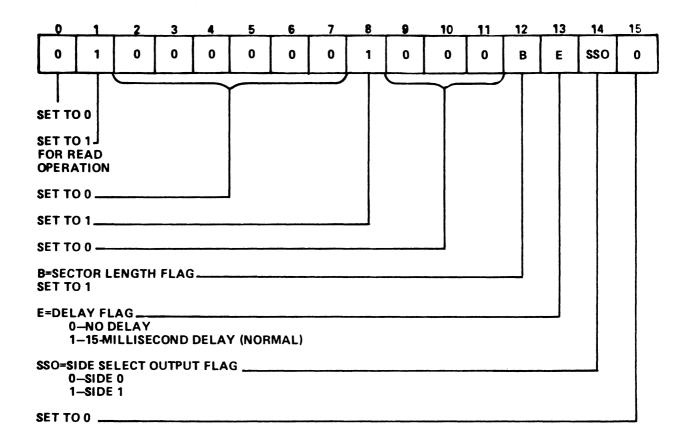

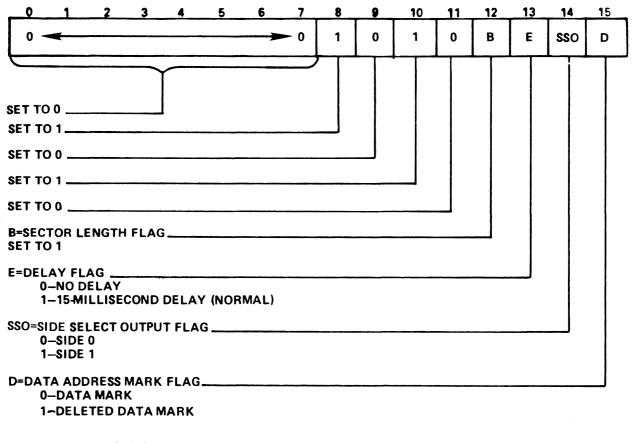

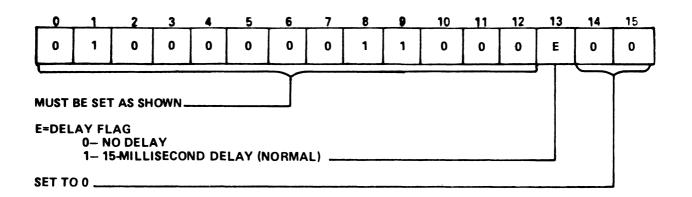

| 5.1<br>5.1.2<br>5.1.3<br>5.2<br>5.3<br>5.3.1<br>5.3.2<br>5.3.2.1<br>5.3.2.2<br>5.3.3<br>5.3.4<br>5.3.5<br>5.3.6<br>5.4<br>5.4.1.1<br>5.4.1.2<br>5.4.1.1<br>5.4.1.2<br>5.4.1.3<br>5.4.1.4<br>5.4.1.5<br>5.4.1.5<br>5.4.1.5<br>5.4.1.5<br>5.4.1.5<br>5.4.1.5<br>5.4.1.5<br>5.4.1.5<br>5.4.1.5<br>5.4.1.5<br>5.4.1.5<br>5.4.1.5<br>5.4.1.5<br>5.4.1.5<br>5.5.1.1<br>5.5.1.1<br>5.5.1.1<br>5.5.1.2<br>5.5.2<br>5.6<br>5.6.1<br>5.6.2 | Restore Command Bit Configuration<br>Seek Command Bit Configuration<br>Status Register<br>Track Register<br>Data Register<br>INPUT/OUTPUT CONTROL BLOCK (IOCB)<br>Command Word (Word 0)<br>Read Sector Command<br>Write Sector Command<br>Read Address Command<br>Read Track Command<br>Write track Command | 5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-12<br>5-13<br>5-14<br>5-15<br>5-16<br>5-17<br>5-21<br>5-21<br>5-22<br>5-23<br>5-23<br>5-24<br>5-31<br>5-32<br>5-32<br>5-31<br>5-32<br>5-34<br>5-35<br>5-36<br>5-38<br>5-38<br>5-39<br>5-38<br>5-39<br>5-39<br>5-38<br>5-39<br>5-38<br>5-39<br>5-39<br>5-38<br>5-39<br>5-39<br>5-38<br>5-39<br>5-38<br>5-39<br>5-39<br>5-39<br>5-38<br>5-39<br>5-39<br>5-39<br>5-39<br>5-38<br>5-39<br>5-39<br>5-39<br>5-39<br>5-38<br>5-39<br>5-39<br>5-39<br>5-39<br>5-38<br>5-39<br>5-39<br>5-39<br>5-39<br>5-38<br>5-39<br>5-39<br>5-39<br>5-39<br>5-38<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-39<br>5-40<br>5-41 |

•

$_{\rm c}\approx 0.05_{\rm M_{\odot}}$

| 6       | MARK 2 DISC/FLOPPY DRIVE INTERFACE    | 6-1  |

|---------|---------------------------------------|------|

| 6.1     | INTRODUCTION                          | 6-1  |

| 6.2     | MARK 2 INTERFACE                      | 6-3  |

| 6.3     | PROGRAMMED INPUT/OUTPUT               | 6-10 |

| 6.3.1   | Data Register                         | 6-11 |

| 6.3.2   | Write Precomp Register                | 6-11 |

| 6.3.3   | Error Register                        | 6-12 |

| 6.3.4   | Sector Count Register                 | 6-15 |

| 6.3.5   | Sector Number Register                | 6-15 |

| 6.3.6   | Cylinder High and Low Registers       | 6-16 |

| 6.3.7   | Select/Drive/Head Register            | 6-17 |

| 6.3.8   | Command Register                      | 6-18 |

| 6.3.8.1 | Test Command Bit Configuration        | 6-18 |

| 6.3.8.2 | Restore Command Bit Configuration     | 6-19 |

| 6.3.8.3 | Seek Command Bit Configuration        | 6-20 |

| 6.3.9   | Status Register                       | 6-21 |

| 6.4     | INPUT/OUTPUT CONTROL BLOCK (IOCB)     | 6-23 |

| 6.4.1   | Opcode/Write Precomp Word (Word 0)    | 6-23 |

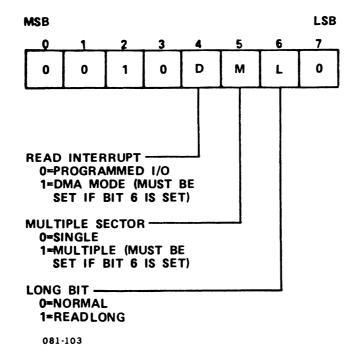

| 6.4.1.1 | Read Sector Command                   | 6-24 |

| 6.4.1.2 | Readlong Command                      | 6-25 |

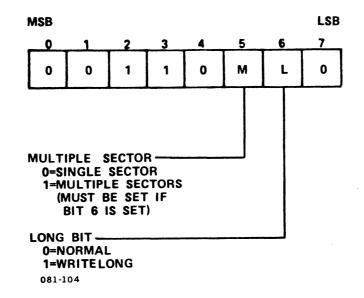

| 6.4.1.3 | Write Sector Command                  | 6-25 |

| 6.4.1.4 | Writelong Command                     | 6-26 |

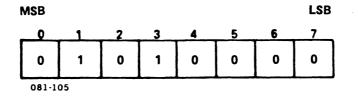

| 6.4.1.5 | Format Track Command                  | 6-26 |

| 6.4.2   | Sector Number and Count Word (Word 1) | 6-27 |

| 6.4.3   | Cylinder Number Word (Word 2)         | 6-27 |

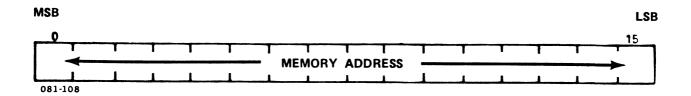

| 6.4.4   | Memory Address Word (Word 3)          | 6-28 |

| 6.4.5   | Termination Status Word (Word 4)      | 6-28 |

### APPENDICES

| Α | ASCII Codes                     | A-1 |

|---|---------------------------------|-----|

| В | Tape Handling Flowcharts        | B-1 |

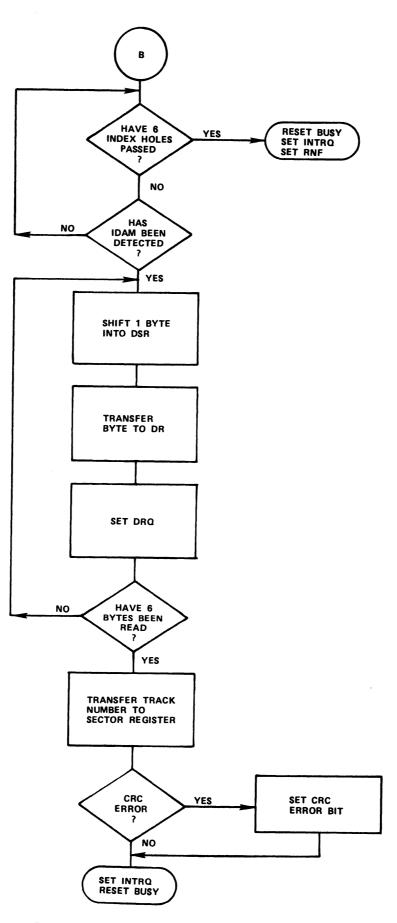

| С | Floppy Disc Handling Flowcharts | C-1 |

### **FIGURES**

### Title

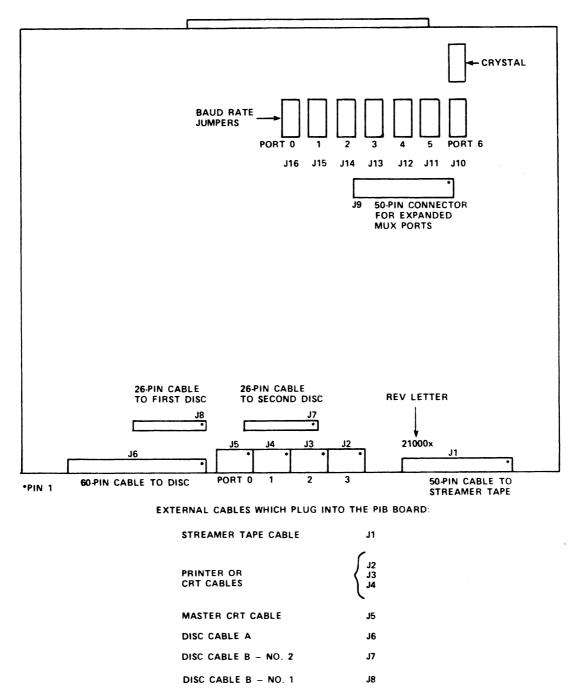

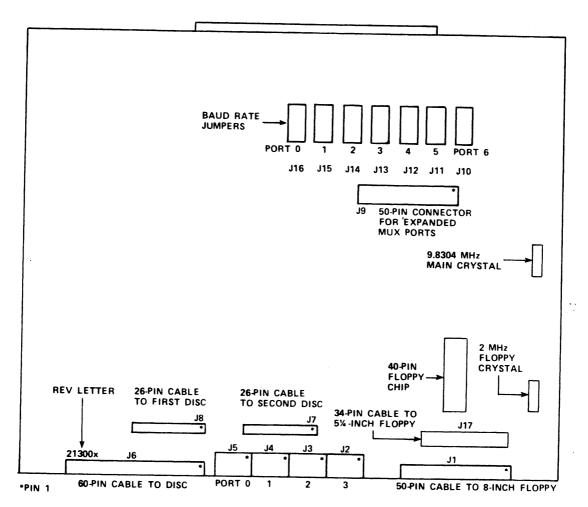

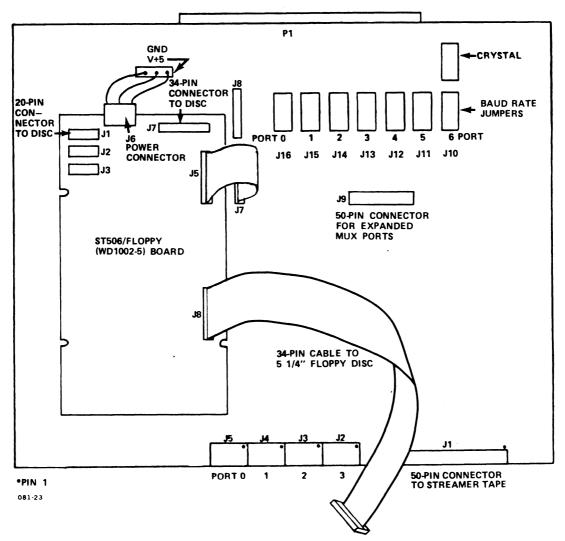

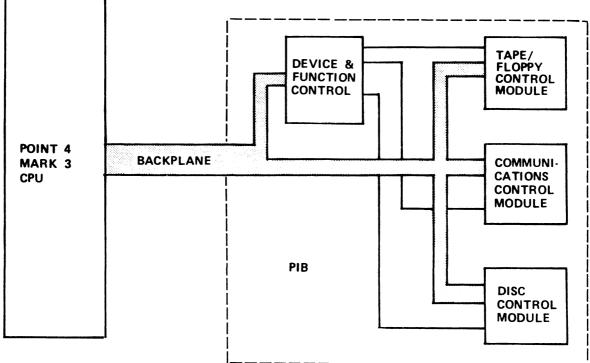

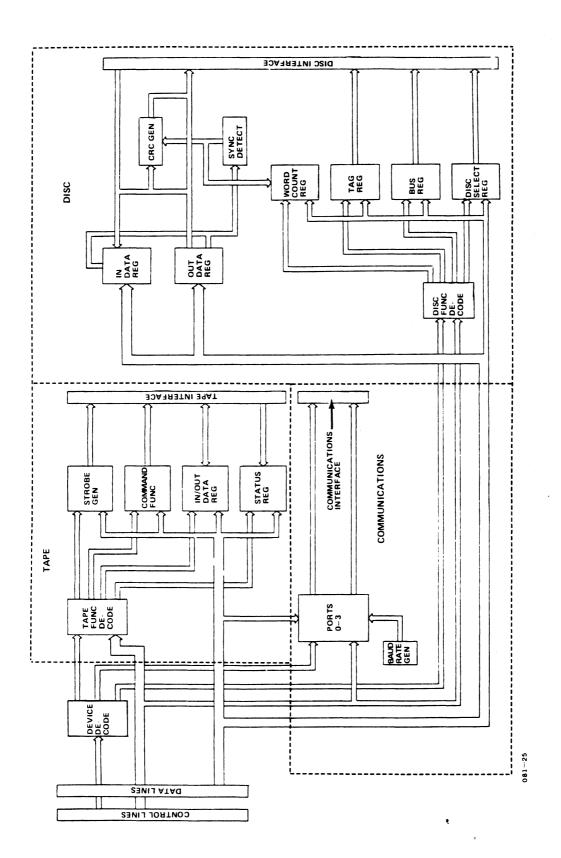

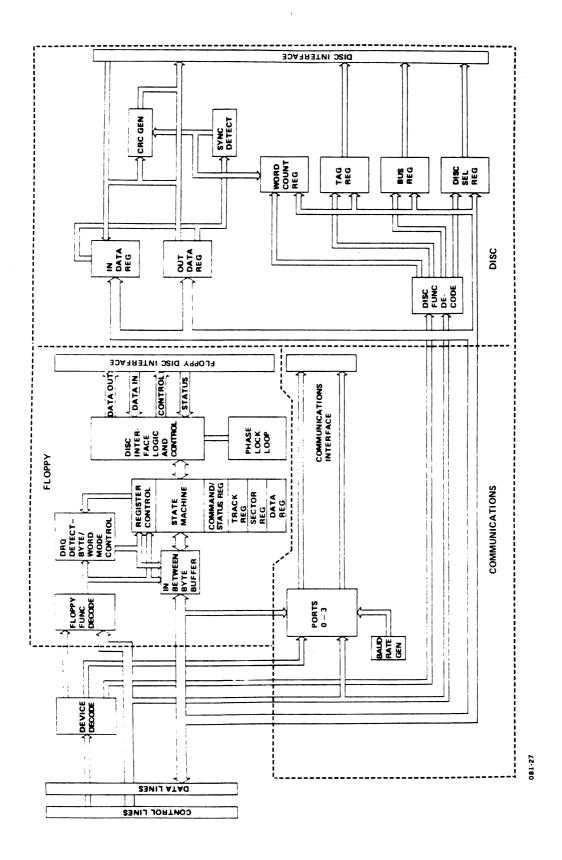

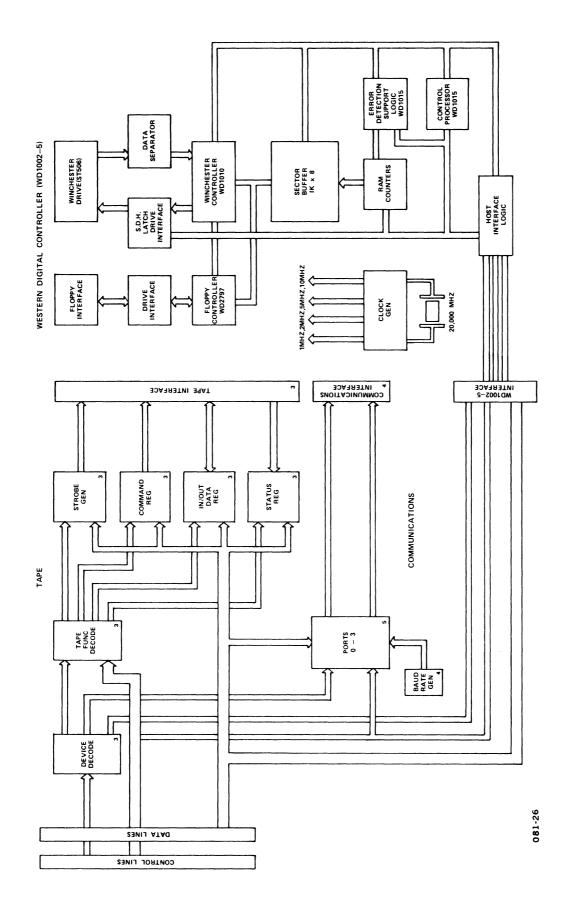

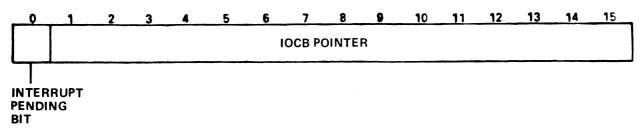

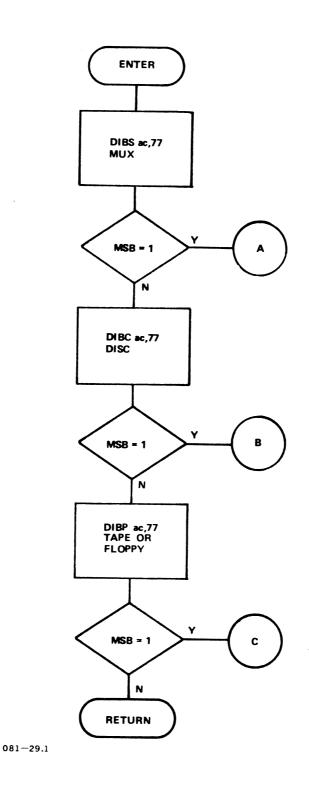

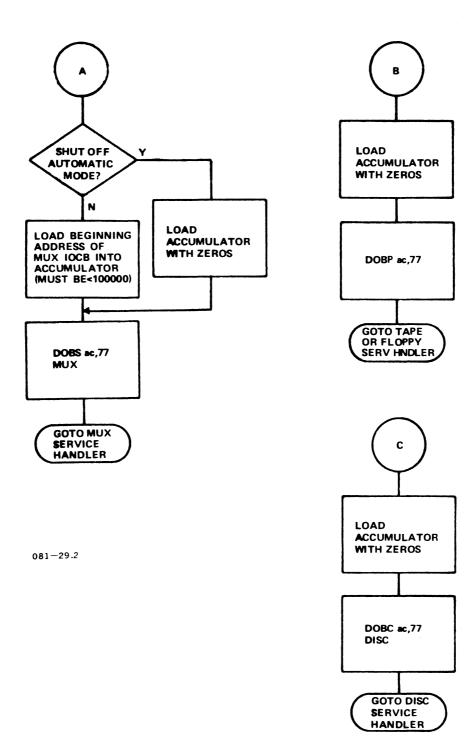

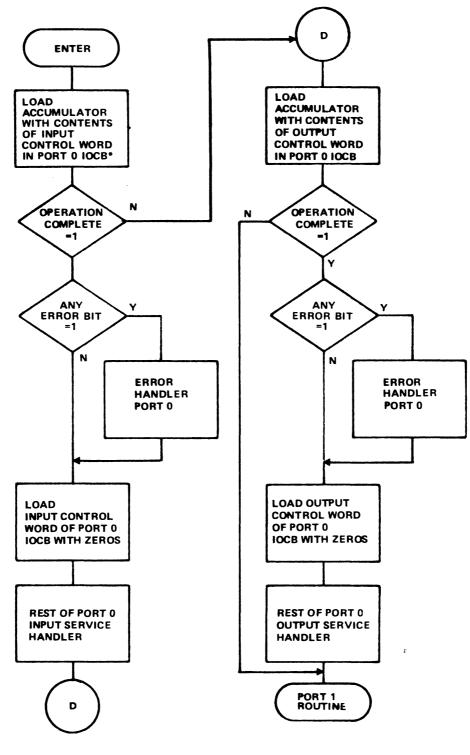

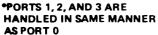

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>1-6<br>1-7<br>1-8<br>1-9<br>1-10<br>1-11 | POINT 4 MARK 3 Peripheral Interface Board<br>POINT 4 MARK 3B Peripheral Interface Board<br>POINT 4 MARK 2 Peripheral Interface Board<br>Peripheral Interface Board System Block Diagram<br>MARK 3 PIB Internal Architecture<br>MARK 3B PIB Internal Architecture<br>MARK 2 PIB Internal Architecture<br>IOCB Pointer Format<br>Software Polling/Interrupt Handling Flowchart<br>I/O Service Routine Multiplexer Handling<br>Procedures<br>I/O Service Routine Disc/Tape/Floppy Handling<br>Procedures | $ \begin{array}{r} 1-3\\ 1-4\\ 1-5\\ 1-7\\ 1-13\\ 1-14\\ 1-15\\ 1-18\\ 1-20\\ 1-23\\ 1-24\\ \end{array} $ |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

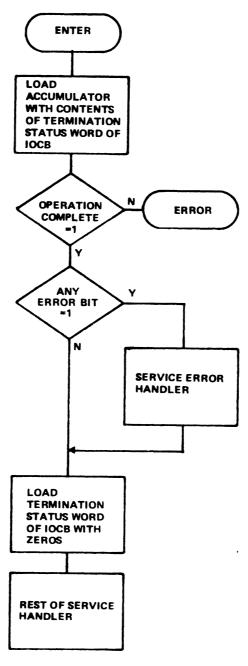

| <b>0</b> 1                                                                  | Paud Data Haadar Lagatiang                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-3                                                                                                       |

| 2-1<br>2-2                                                                  | Baud Rate Header Locations<br>Command Register                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-3                                                                                                       |

| 2-2                                                                         | Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-8                                                                                                       |

| 2-4                                                                         | Software Polling Flowchart for                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20                                                                                                        |

|                                                                             | Output Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-11                                                                                                      |

| 2-5                                                                         | MUX Input/Output Control Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-13                                                                                                      |

| 2-6                                                                         | Input Control Word - Word 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-14                                                                                                      |

| 2-7                                                                         | Output Control Word - Word 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-20                                                                                                      |

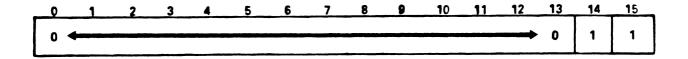

| 2-8                                                                         | Master Reset Instruction Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-28                                                                                                      |

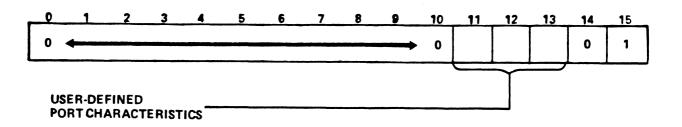

| 2-9                                                                         | Port Initialization Instruction Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-29                                                                                                      |

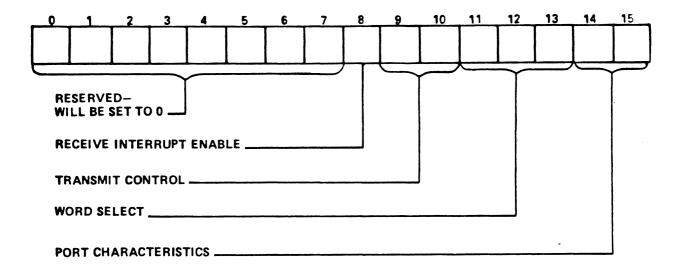

| 2-10                                                                        | Transmitter/Receiver Instruction Format                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-30                                                                                                      |

| 3-1<br>3-2                                                                  | Daisy Chain Drive Connection<br>PIB/Disc Drive Differential Bus Signals                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-3<br>3-5                                                                                                |

| 3-3                                                                         | PIB/Disc Drive Differential Synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                           |

|                                                                             | Cable Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-9                                                                                                       |

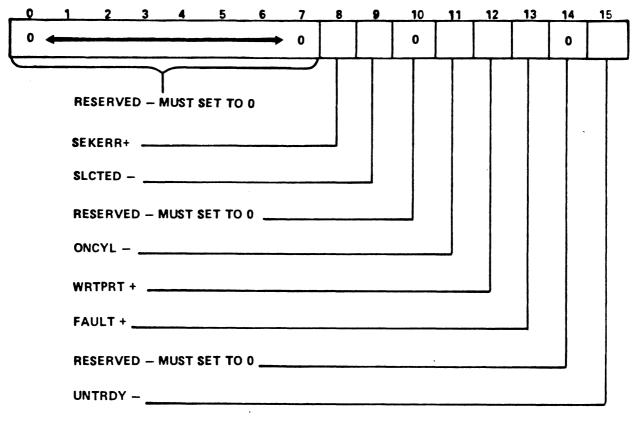

| 3-4                                                                         | Drive Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-11                                                                                                      |

| 3-5                                                                         | Contents of DOA Instruction Accumulator                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-14                                                                                                      |

| 3-6                                                                         | Tag 1 Instruction Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-16                                                                                                      |

| 3-7                                                                         | Tag 2 Instruction Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-17<br>3-18                                                                                              |

| 3-8<br>3-9                                                                  | Tag 3 Instruction Format<br>Disc IOCB Format                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-18                                                                                                      |

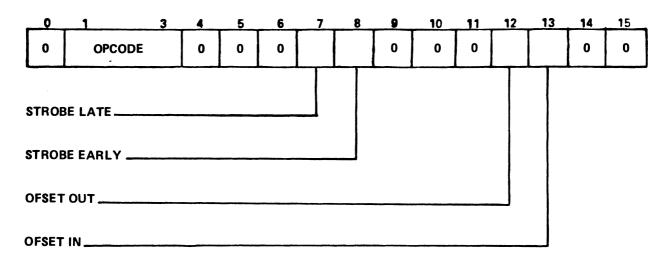

| 3-10                                                                        | Opcode Word Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-20                                                                                                      |

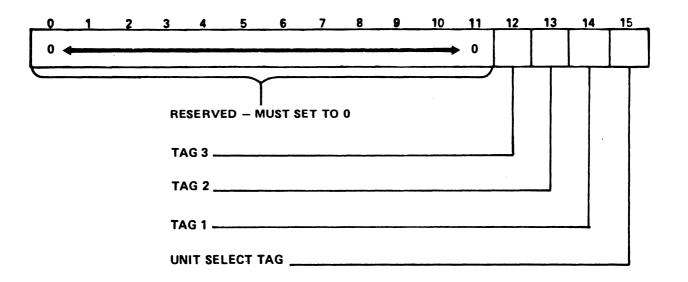

| 3-11                                                                        | Unit Number Word Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-21                                                                                                      |

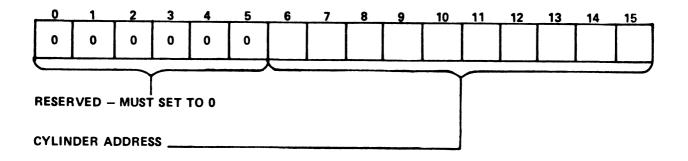

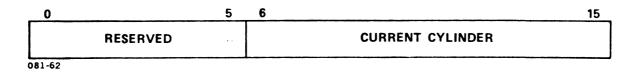

| 3-12                                                                        | Cylinder Address Word Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-22                                                                                                      |

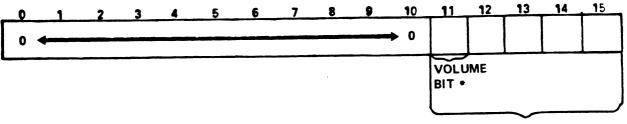

| 3-13                                                                        | Head/Volume Word Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-23                                                                                                      |

| 3-14                                                                        | Sector Address Word Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-24                                                                                                      |

| - 3-15                                                                      | Sector Count Word Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-25                                                                                                      |

| 3-16                                                                        | Memory Address Word Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-26                                                                                                      |

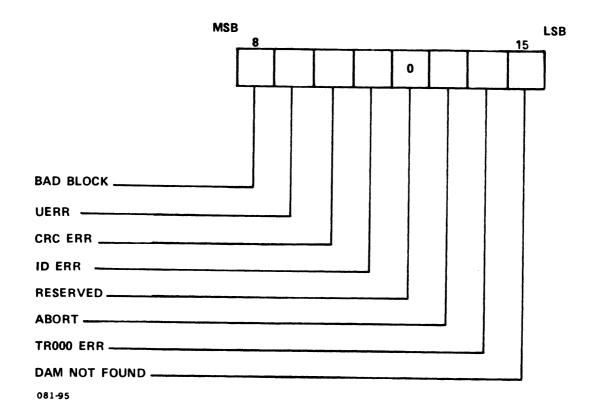

| 3-17                                                                        | Termination Status Word Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-27                                                                                                      |

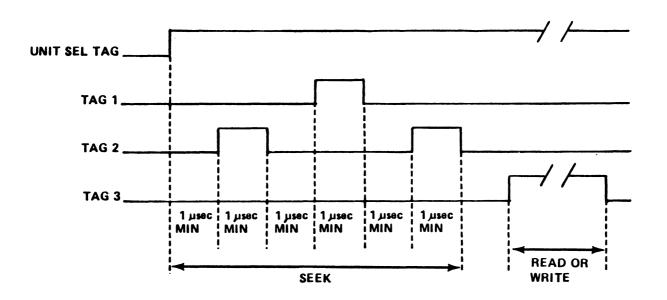

| 3-18                                                                        | Seek Operation Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-32                                                                                                      |

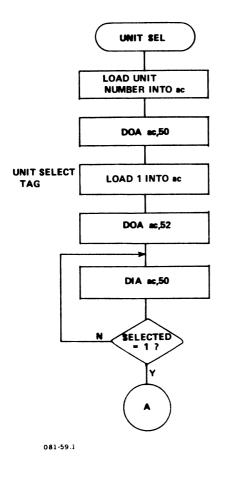

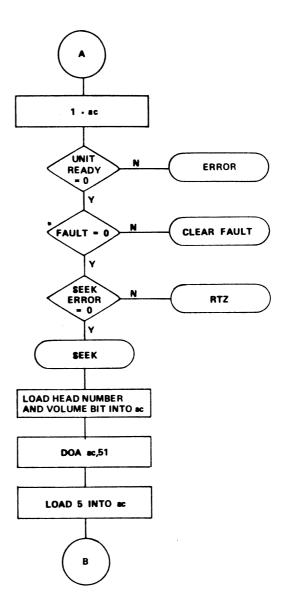

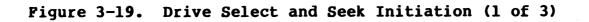

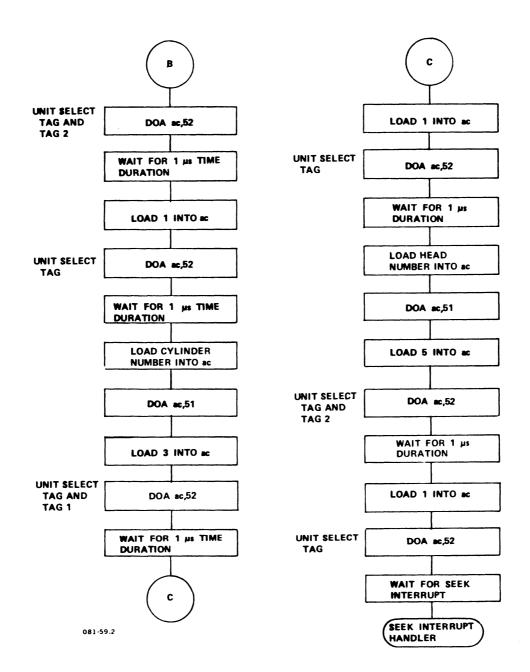

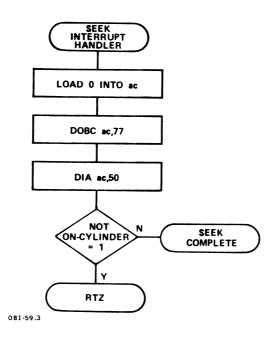

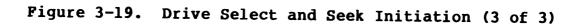

| 3-19                                                                        | Drive Select and Seek Initiation                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-33                                                                                                      |

| 3-20                                                                        | Seek Error Recovery Flowchart                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-38<br>3-39                                                                                              |

| 3-21                                                                        | Sector Table in Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-33                                                                                                      |

REPER

| 3-22<br>3-23<br>3-24<br>3-25<br>3-26<br>3-27<br>3-28                                      | Sector Block Format - Word O Contents<br>Sector Block Format - Word 1 Contents<br>Sector Block Format - Word 2 Contents<br>Sector Block Format - Word 3 Contents<br>Input/Output Control Block<br>First Sector Block<br>Read-Regardless Operation                                                                                                                                                                                                                     | 3-40<br>3-41<br>3-42<br>3-43<br>3-44<br>3-44<br>3-48                                                         |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

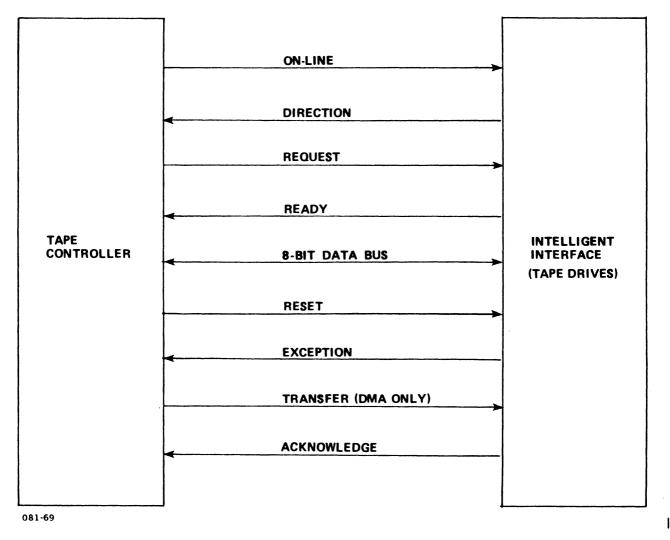

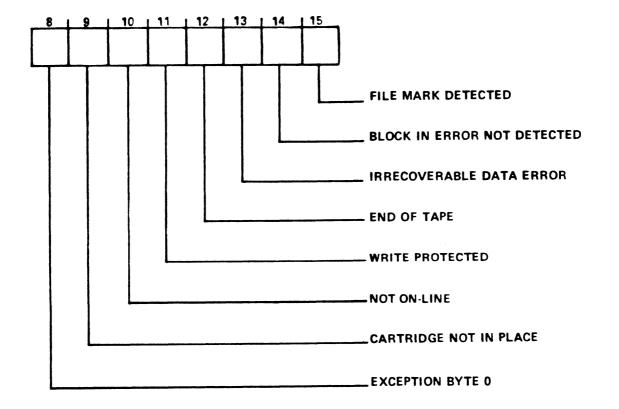

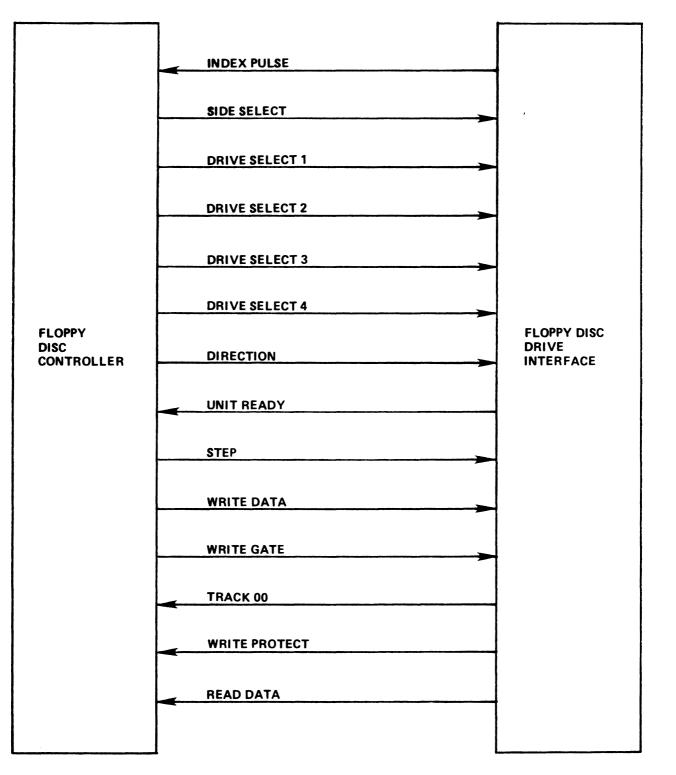

| 4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7                                             | Tape Controller Interface Signals<br>Format of DIA Instruction Accumulator<br>Contents of DOA Instruction Accumulator<br>Tape Controller IOCB Format<br>Tape Controller Command Format<br>Exception Byte 0<br>Exception Byte 1                                                                                                                                                                                                                                        | 4-3<br>4-7<br>4-10<br>4-13<br>4-16<br>4-24<br>4-27                                                           |

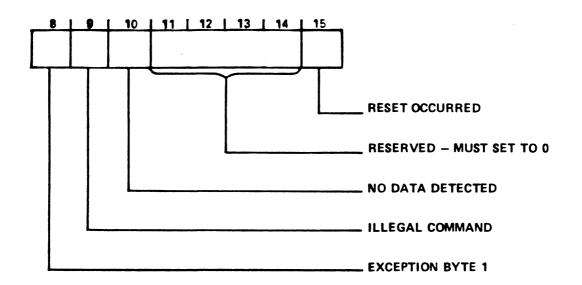

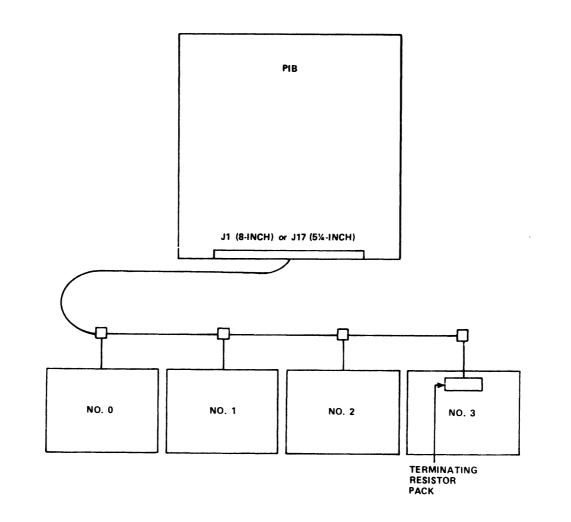

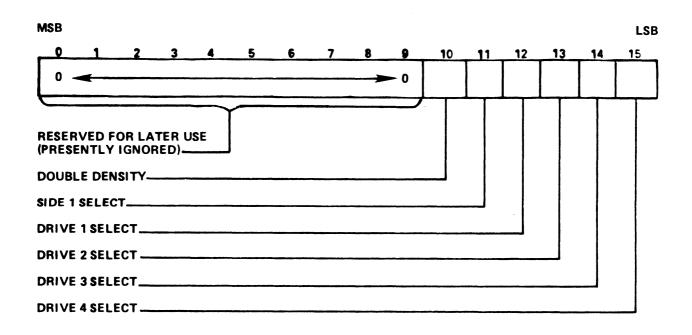

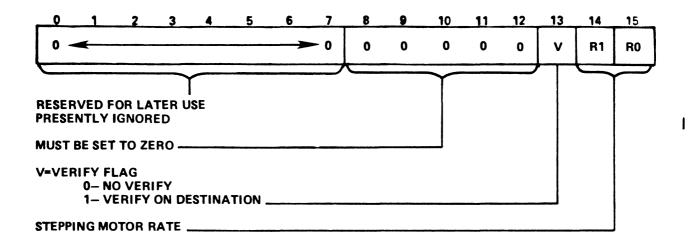

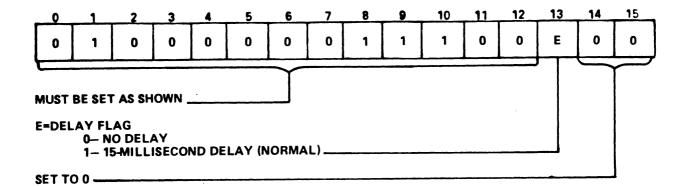

| 5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6                                                    | Daisy-Chain Drive Connection<br>PIB/Floppy Disc Drive Interface Signals<br>Select Register Word<br>Restore Command Bit Configuration<br>Seek Command Bit Configuration<br>Drive Status Register Word For Data Transfer                                                                                                                                                                                                                                                | 5-5<br>5-6<br>5-13<br>5-15<br>5-16                                                                           |

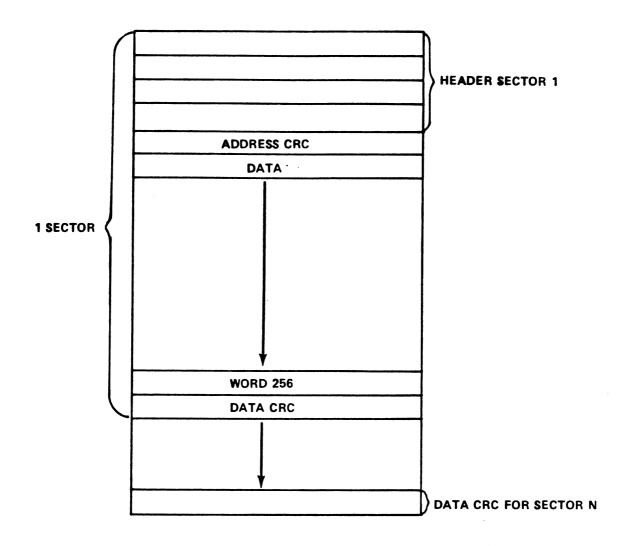

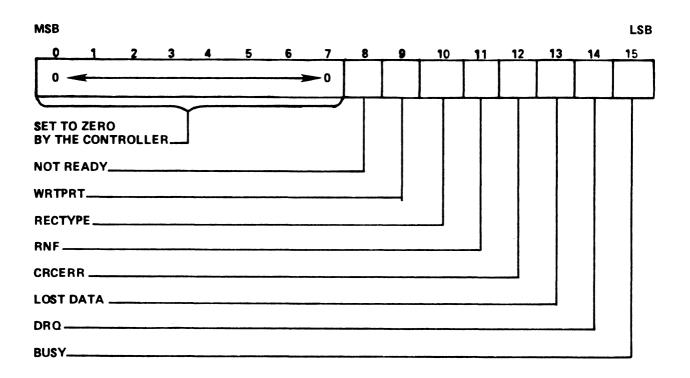

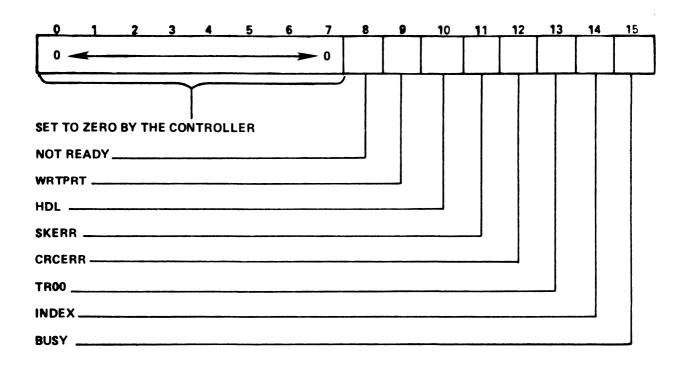

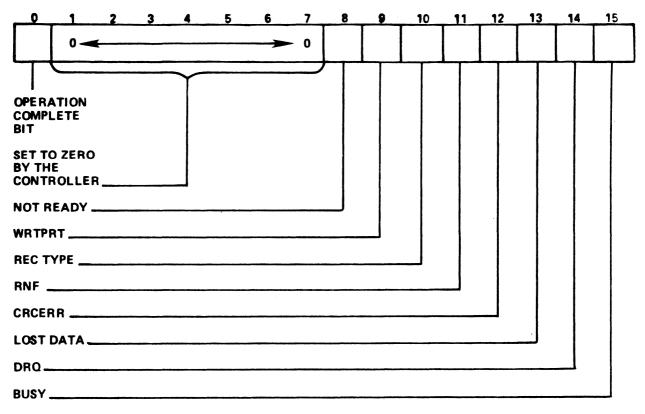

| 5-7<br>5-8<br>5-9<br>5-10<br>5-11<br>5-12<br>5-13<br>5-14<br>5-15<br>5-16<br>5-17<br>5-18 | Commands<br>Status Register For Head Movement Commands<br>Floppy Disc IOCB Format<br>Read Sector Command Word Bit Configuration<br>Write Sector Command Word Bit Configuration<br>ID Field<br>Read Address Command Word Bit Configuration<br>Read Track Command Word Bit Configuration<br>Write Track Command Word Bit Configuration<br>Memory Address Word Bit Configuration<br>Termination Status Word Format<br>Seek Operation Flowchart<br>512-Byte Sector Format | 5-17<br>5-19<br>5-23<br>5-25<br>5-27<br>5-29<br>5-29<br>5-30<br>5-31<br>5-32<br>5-32<br>5-32<br>5-37<br>5-40 |

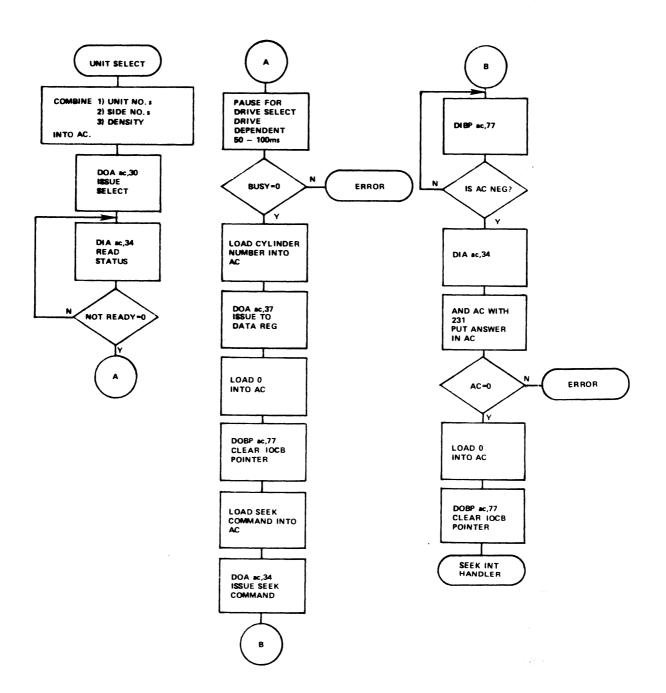

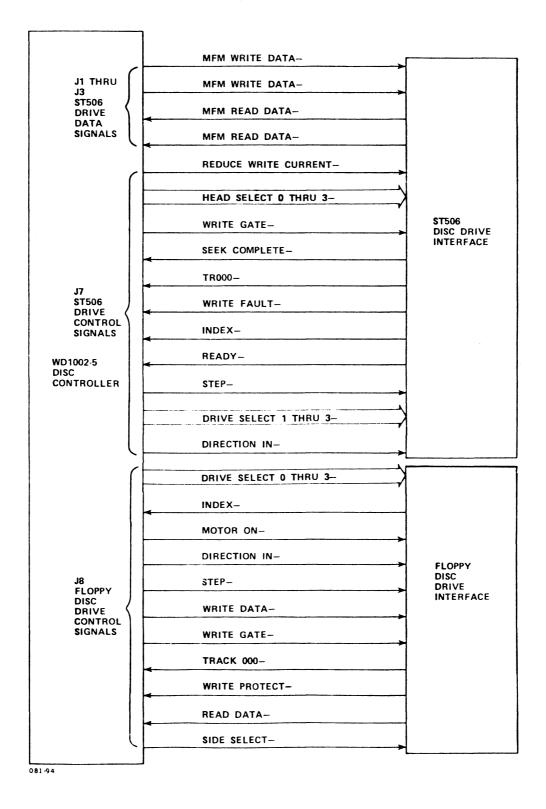

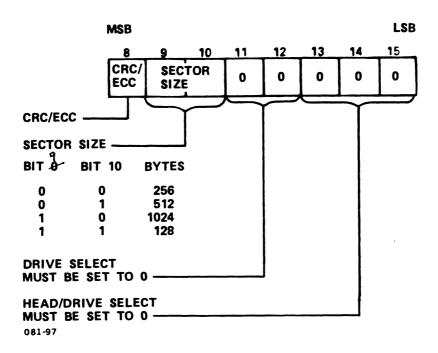

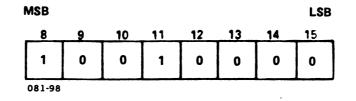

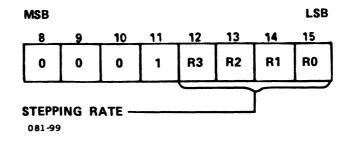

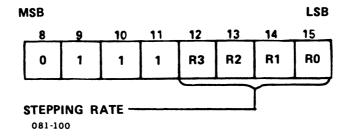

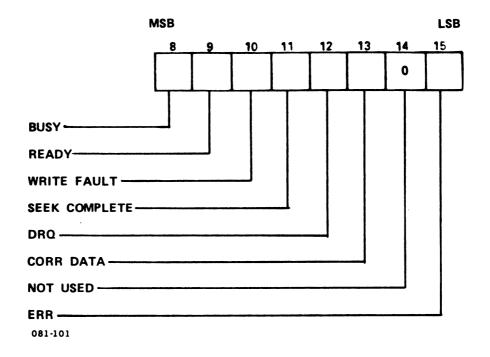

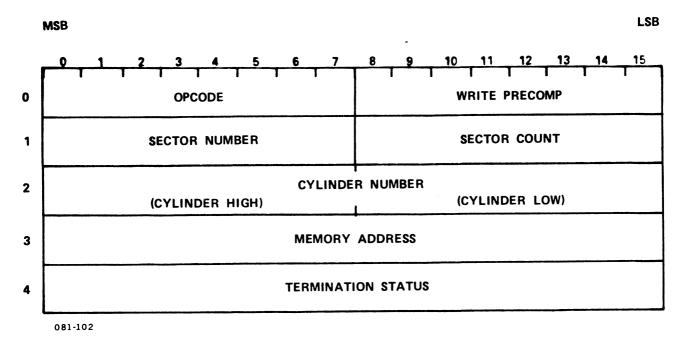

| 6-1<br>6-2<br>6-3<br>6-4<br>6-5<br>6-6<br>6-7<br>6-8<br>6-9<br>6-10                       | WD1002-5 Disc Controller Interface Signals<br>Error Register Bit Configuration<br>Low-High Cylinder Registers and Cylinder Number<br>SDH Register Bit Configuration<br>Test Command Bit Configuration<br>Restore Command Bit Configuration<br>Seek Command Bit Configuration<br>Status Register Bit Configuration<br>ST506 Disc IOCB Format<br>Read Sector/Readlong Command Bit Configuration                                                                         | 6-4<br>6-13<br>6-16<br>6-17<br>6-18<br>6-19<br>6-20<br>6-21<br>6-23<br>6-24                                  |

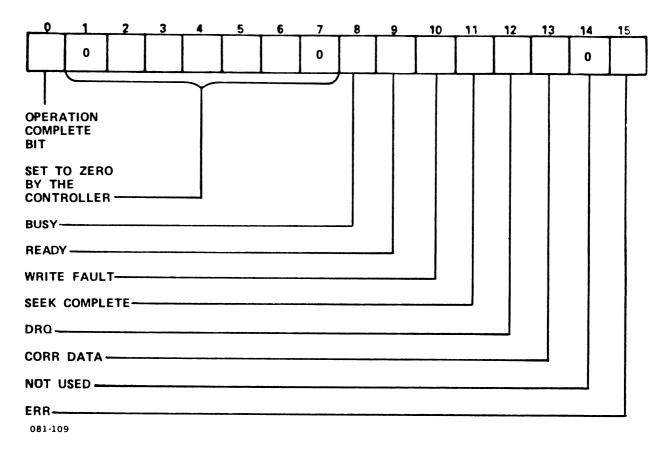

| 6-11<br>6-12<br>6-13                                                                      | Write Sector/Writelong Command Bit<br>Configuration<br>Format Track Command Bit Configuration<br>Sector Number and Count Bit Configuration                                                                                                                                                                                                                                                                                                                            | 6-25<br>6-26                                                                                                 |

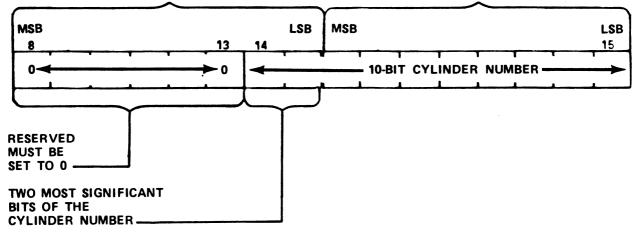

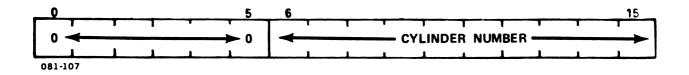

| 6-14                                                                                      | (Word l of IOCB)<br>Cylinder Number Bit Configuration<br>(Word 2 of IOCB)                                                                                                                                                                                                                                                                                                                                                                                             | 6-27<br>6-27                                                                                                 |

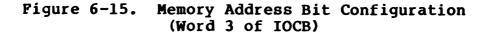

| 6-15                                                                                      | Memory Address Bit Configuration<br>(Word 3 of IOCB)                                                                                                                                                                                                                                                                                                                                                                                                                  | 6-28                                                                                                         |

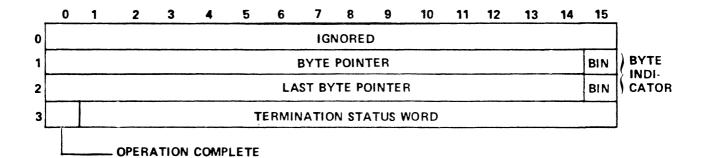

| 6-16                                                                                      | Termination Status Bit Configuration<br>(Word 4 of IOCB)                                                                                                                                                                                                                                                                                                                                                                                                              | 6-28                                                                                                         |

| HM-081-0<br>POINT 4                                                                       | 027-D<br>Data Corporation xiii MARK 2/3 Peripherals                                                                                                                                                                                                                                                                                                                                                                                                                   | Manual                                                                                                       |

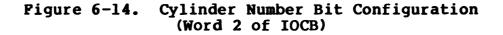

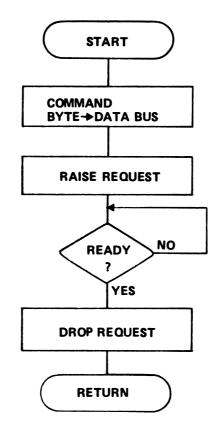

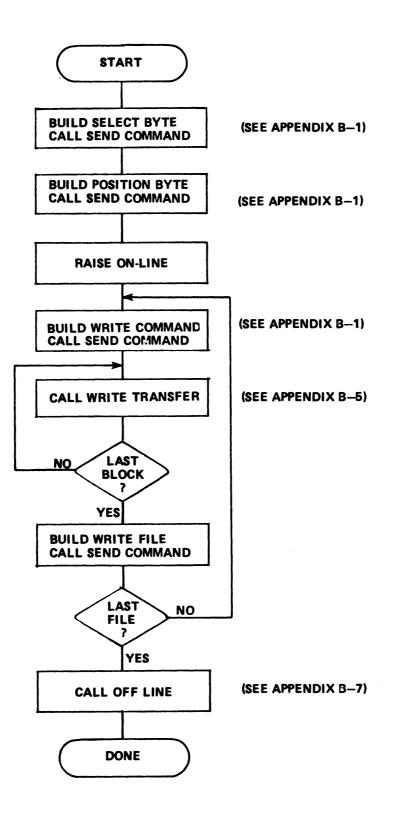

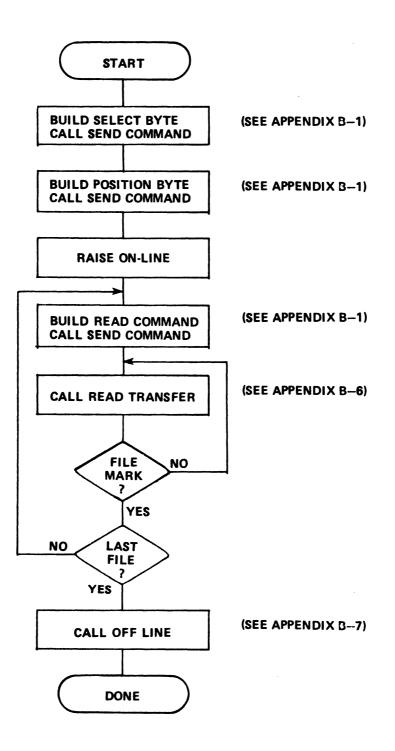

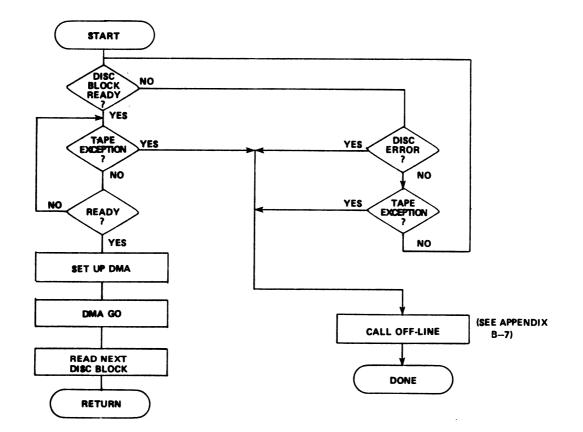

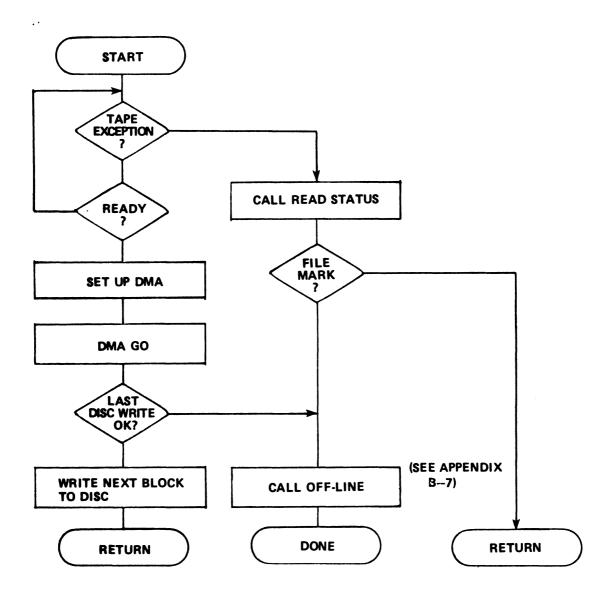

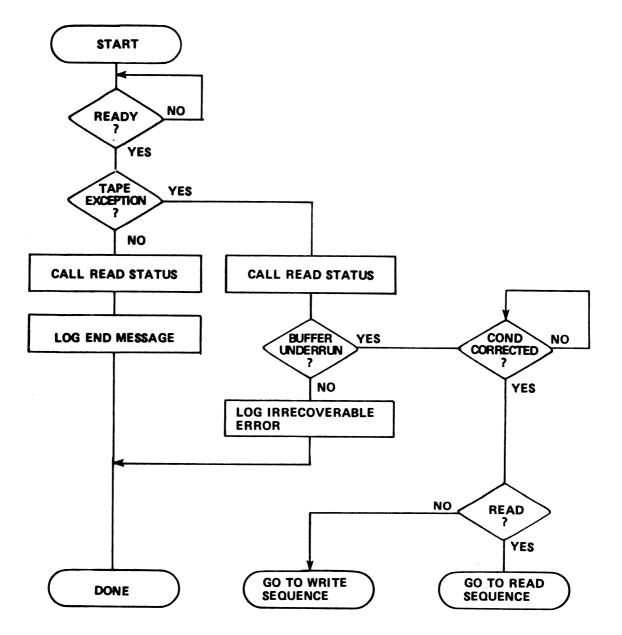

| B-1<br>B-2<br>B-3<br>B-4<br>B-5<br>B-6<br>B-7 | (Tape Flowcharts)<br>Command Transfer Sequence Flowchart<br>Read Status Sequence Flowchart<br>Write Sequence Flowchart<br>Read Sequence Flowchart<br>Write Transfer Sequence Flowchart<br>Read Transfer Sequence Flowchart<br>Off-line Sequence Flowchart | B-2<br>B-3<br>B-4<br>B-5<br>B-6<br>B-7<br>B-8 |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

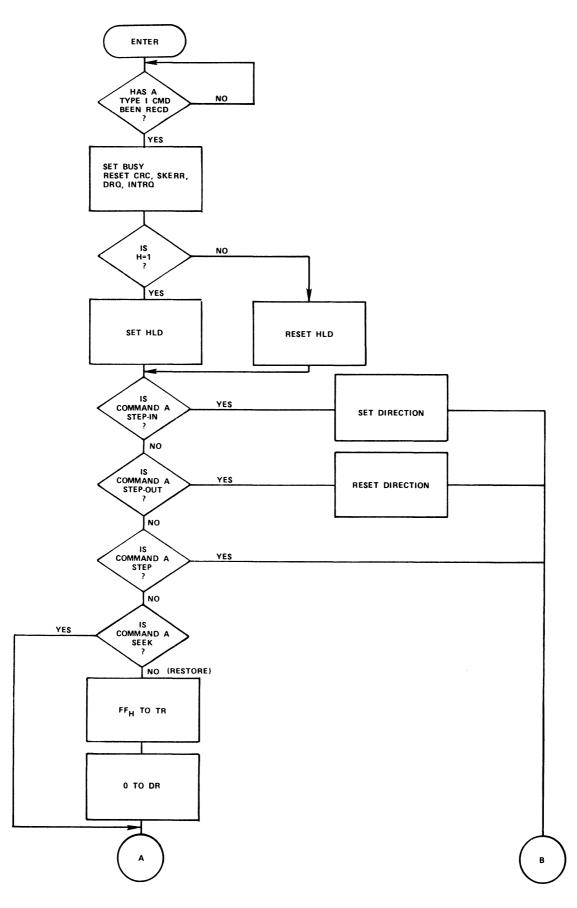

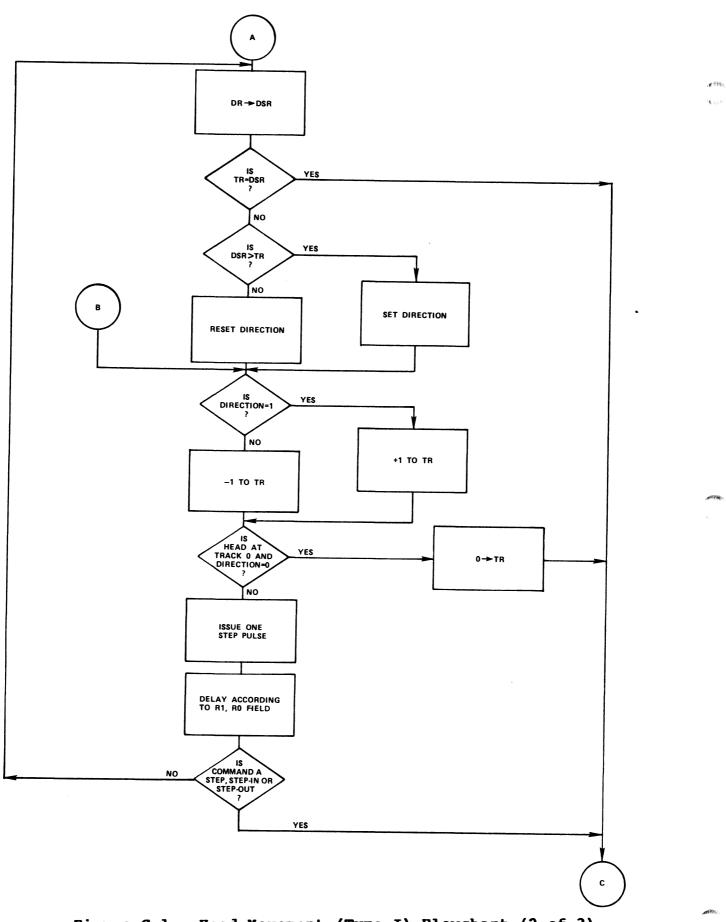

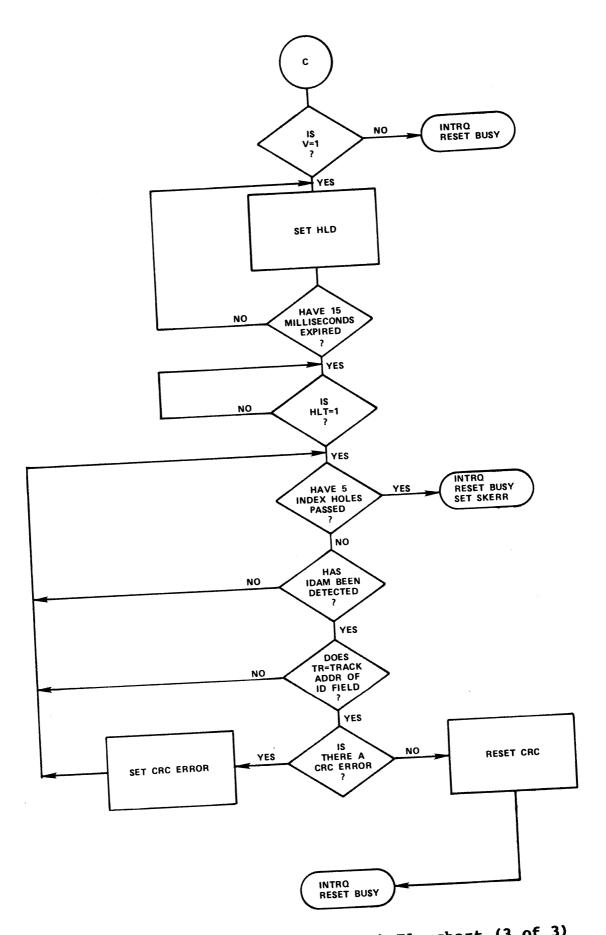

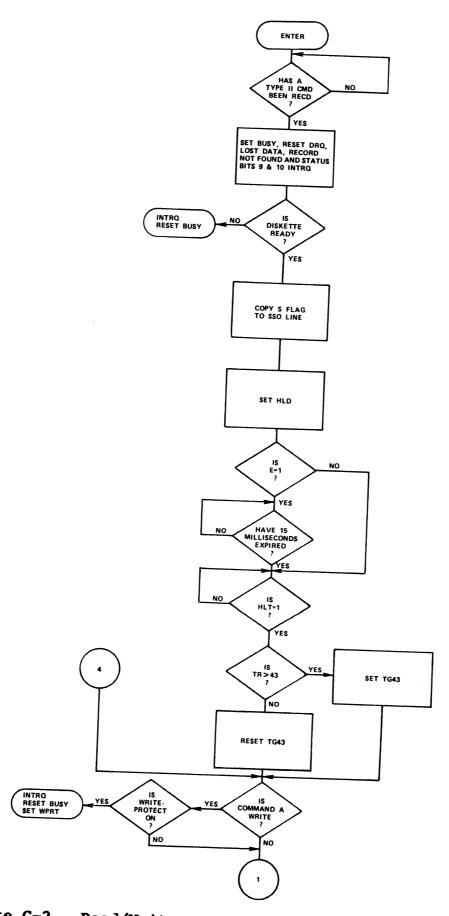

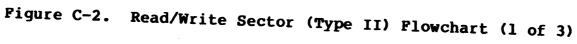

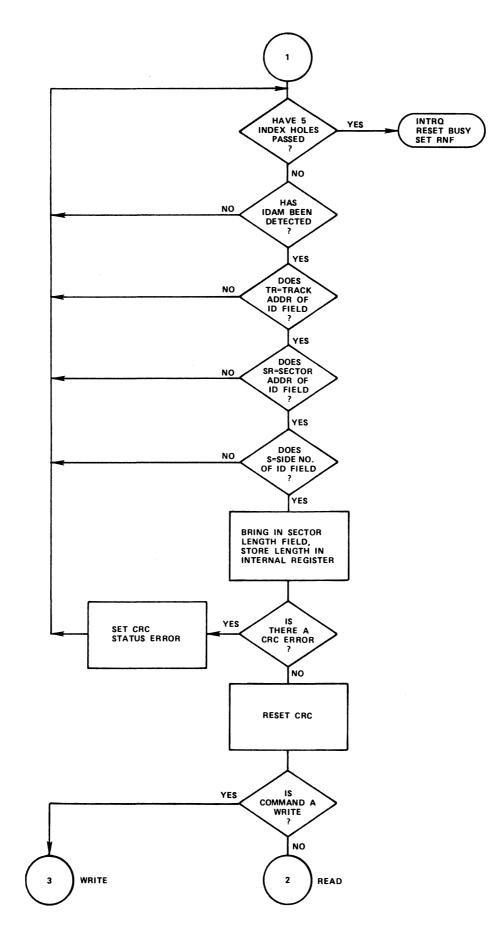

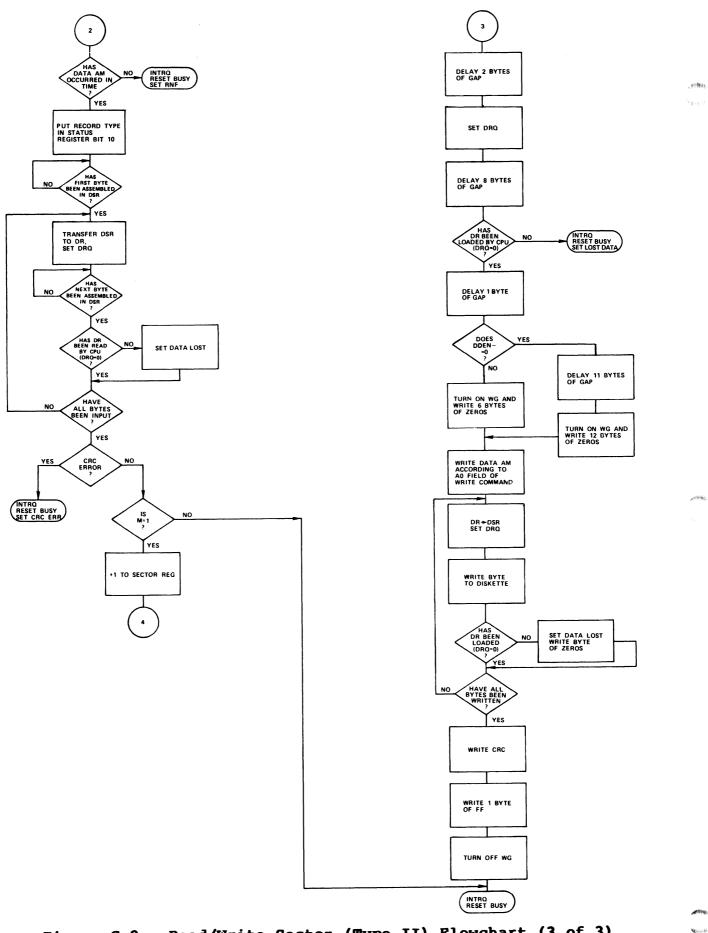

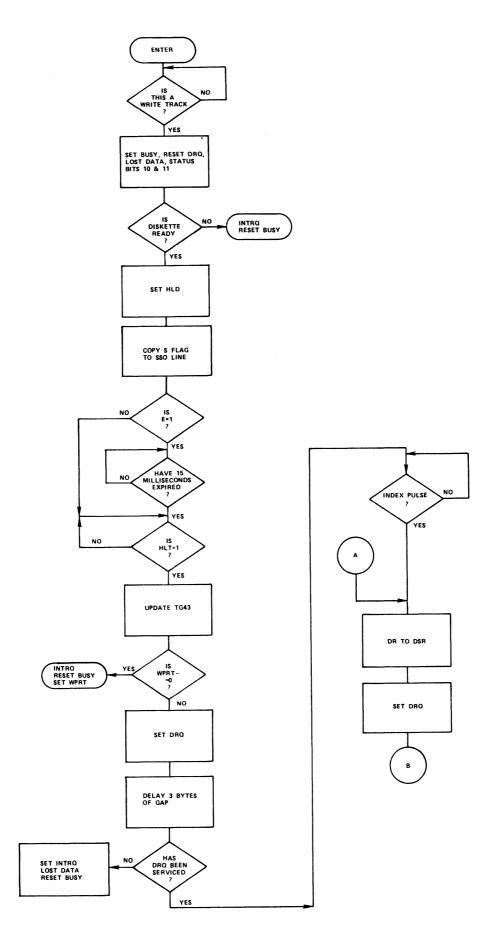

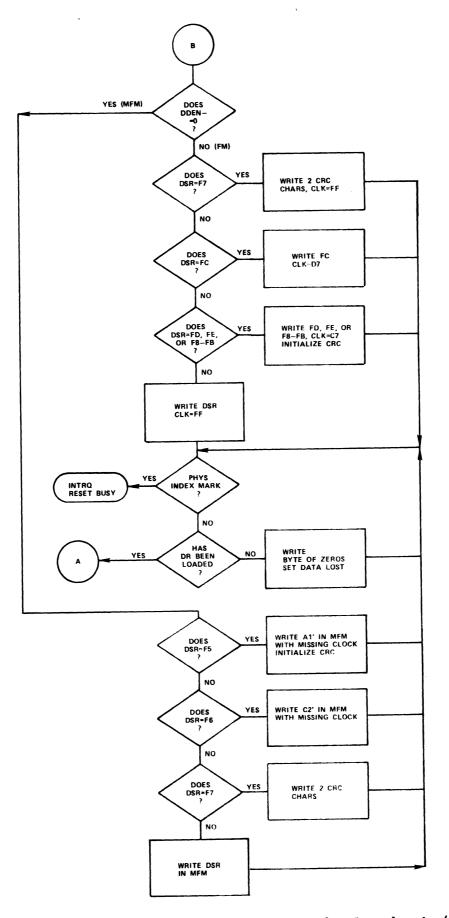

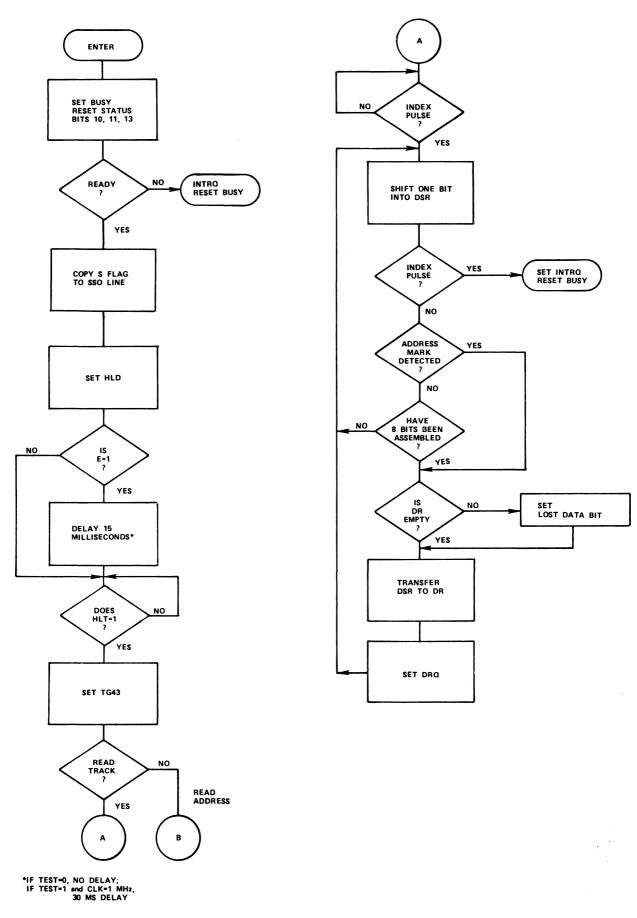

| C-1<br>C-2<br>C-3<br>C-4                      | (Floppy Disc Flowcharts)<br>Head Movement (Type I) Flowchart<br>Read/Write Sector (Type II) Flowchart<br>Write Track (Type III) Flowchart<br>Read Track/Read Address (Type III) Flowchart                                                                 | C-3<br>C-6<br>C-9<br>C-11                     |

### TABLES

### Number

### Title

### Page

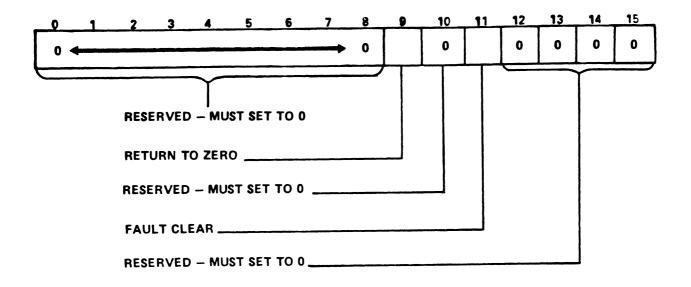

2 - 22-1 Baud Rate Jumpering 2-2 Port Assignments for Baud Rate Headers 2-2 2-4 2-3 DOA, DIA Device Codes 2-6 2 - 4Command Register Bit Functions 2-9 2-5 Status Register Bit Operations 2 - 6Input Control Word Definitions (Word 0 of Each Control Block) 2-15 2-7 Output Control Word Definitions 2-21 (Word 1 of Each Control Block) 2-31 2 - 8Enabling/Disabling Operation 3-1 Disc Drive Differential Bus Signals (A Cable Pin Assignment) 3-6 3-10 Drive Synchronization Cable Signals 3-2 3-12 3-3 Drive Status Definitions 3-15 3 - 4DOA Instruction Accumulator Bits 3-5 Data Bus Bit Functions with Tag 1 3-16 Data Bus Bit Functions with Tag 2 3 - 173-6 3-18 3-7 Data Bus Bit Functions with Tag 3 3-20 3-8 Disc IOCB Word 0 Disc IOCB Word 1 3-21 3-9 Disc IOCB Word 2 3-22 3-10 3-23 Disc IOCB Word 3 3-11 3 - 243 - 12Disc IOCB Word 4 Disc IOCB Word 5 3-25 3-13 Disc IOCB Word 6 3-26 3-14 Disc Termination Status Word 7 3-28 3-15 Sector Block Format - Word 0 Functions 3-40 • 3-16

xiv

| HM-081 | -0 | 027-0 | 2           |